Ltspice xvii

Author: h | 2025-04-23

LTspice XVII: Subcircuit pin names in Operating Point analysis. 2. LTspice XVII solving Thevenin Resistance basics. 0. Add LTspice IV library to LTspice XVII. 0. LTSpice:

LTspice XVII - Q A - EngineerZone

The VDMOS model as used in LTspice simulator can model power MOSFET's nicely. Mike Engelhardt updated the VDMOS (May 2019) to include temperature parameters. I have updated my earlier IRF's and Exicon lateral's. They can be downloaded here for LTspice XVII OR LT-IV here. Updated Tutorial PDF for extracting parameters for the IRFP240 and IRFP9240. Download PDF below. A simple jig does pulse measurements (DIY breadboard it - may need Scope). Download PDF below. To simulate CMOS inverters eg for guitar overload effects then you need to use a MOSFET model with quasisaturation. The LTspice VDMOS lacks quasisaturation. It can be added using a subcircuit. Download PDF below. BTW SuperSpice already has a VDMOS with quasisaturation. My files are also provided free under Creative Commons 4 Attribution (over-riding my Copyright) and no liability is accepted. Please let me know if you find errors (use Contact). LTspice jigs for the 'VDMOS parameter extraction' Tutorial PDF (Part 1), Download "Compare-Extraction-jigs-IRFP240-IRFP9240.zip" has 6 LTspice jigs here. Part 1 only (1v6) Hegglun_VDMOS-parameter-extraction-Part- Adobe Acrobat Document 640.9 KB Part 1+2 (version 1v7) Hegglun_VDMOS-parameter-extraction-Part- Adobe Acrobat Document 1.3 MB Pulse tester jig Ver 1v0 Hegglun_Simple-pulse-jig-for-power-MOSFE Adobe Acrobat Document 441.2 KB LTspice files below for the 'Simple pulse jig for power MOSFETs' : Download "VDMOS+EKV-10x20+20x20" LTspice jigs and Spreadsheet here. Download "VDMOS-20N20+20P20-measured-data" here. Dec 2021 superseded: Subcircuit to add Quasisaturation to the VDMOS (Ver 0v1) white paper here and LTspice demo files here Triode+SIT+jFET subcircuit using the VDMOS Dec 2021: This is an ambitious subcircuit! I may change it into 3 separate versions some day. updated white paper here. models and demo jig here. Update Jan 2023 This VDMOS subcircuit models jFET's, SIT's and Triode's, it adds effects including: Gate-drain leakage current (IGSX) that changes with Vds and temperature Quasisaturation for jFET's is significant for most small-signal jFET plots Noise and breakdown parameters are also included Triode (SIT) Mu varies with Vgk (Vgs) and Vak (Vds), and Triode positive grid current is modulated by Vak Update Jan 2023 TriJmos-Triode-and-jFET-model-using-the- Adobe Acrobat Document 839.7 KB

Thevenin Resistance with LTspice XVII

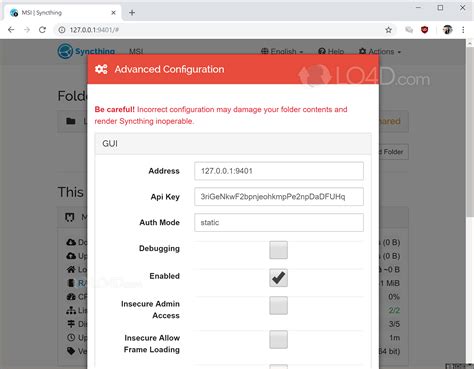

Object such as alist or a generator as a second argument.When the run_all() method is called, it will make run a simulation per each combination of values. On the example aboveit will make the simulations:(XU1, V1) in (("AD712", 5), ("AD712", 10), ("AD712", 15), ("AD820_ALT", 5), ("AD820_ALT", 10), ("AD820_ALT", 15))It should be noted that for each sweep method added it will add a new dimension simulation space.In other words, the total number of simulations will be the product of each vector length. There is no restriction tothe number of simulations to be done, however, a huge number of simulation will take a long time to execute and mayoccupy a considerable amount of space on the disk.Simulators and Windows, Linux and MacOS compatibilityThe LTspice class tries to detect the correct path of the LTspice installation depending on the platform. On Linuxit expects LTspice to be installed under wine. On MacOS, it first looks for LTspice installed under wine, and when itcannot be found, it will look for native LTspice. The reason is that the command line interface of the native LTspice isseverely limited.If you use the native LTspice, please make sure that you have installed the libraries via Settings: Operationtab, Model Update button.Ngspice runs natively under Windows, Linux and MacOS (via brew). This library works with Ngspice CLI, and tries todetect the correct executable path, no matter the platform. It cannot (yet) work with the shared library version ofNgspice that is delivered with for example Kicad, you will need to install the CLI version. You can however use Kicad asthe schema editor and subsequently save the Ngspice netlist to use it with this library.For the other simulators, built-in Linux/MacOS support is coming, but you can always try to use it under Linux viasetting of the executable paths.Executable and Library pathsA large varietyThe LTspice XVII Simulator - Elektor

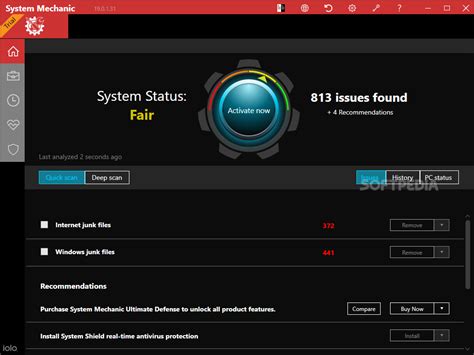

LibreOffice LibreOffice for PC Windows (7/10/11) is a great office suite; its fresh interface, as well as its controlling tools, allows you to release your creativity plus raise your output. LibreOffice includes numerous applications that make it an influential Free & Open Source Office Suite on the market: Writer, the word processor, Calc, the worksheet application, Impress, the performance engine, Draw, our sketch plus flowcharting application, Base, our list and file fronted, besides Math for LTspice LTspice is a freeware utility for assisting professionals or even novice students on how to simulate and regulate circuits. The high-performance simulator, schematic capture, and waveform viewer offer multiple tools for adding geometric shapes to increase the complexity of your object. LTspice Features Smooth Simulation LTspice provides a great variety of macro models for adding to a circuit such as resistors, inductors, capacitors, diodes, wires, BUS taps, text boxes, labels, Microsoft Word Microsoft Word is a powerful text editing platform that offers seamless services for creating, editing, and sharing documents on any device. It is the #1 text editing software and is used by a large community of bloggers, writers, journalists, project managers, and so on. In our day-to-day professional life, we have to do multiple documentation-related tasks, so we need software that reliably performs multiple tasks simultaneously such as text editing, formatting, collaboration,. LTspice XVII: Subcircuit pin names in Operating Point analysis. 2. LTspice XVII solving Thevenin Resistance basics. 0. Add LTspice IV library to LTspice XVII. 0. LTSpice: LTspice 2025 (Bản chuẩn cuối) - Download; LTspice xvii build oct 31 2025 - Download; LTspice xvii build sep 5 2025 - Download; LTspice xvii buildImport LM358 model into LTspice XVII

Today’s electronics systems require an increasing number of power rails and supply solutions, with the load range from a few mA for standby supply to over 100A for ASIC or FPGA core voltage regulators. It is important to have the appropriate solutions for the targeted applications and meet specified performance requirements, such as high efficiency, high reliability, tight printed circuit board (PCB) space, accurate output regulation, fast transient response, and low solution cost. Power management design, especially embedded switching mode supply design, is becoming a more frequent and challenging task for system designers, who may or may not have strong power supply backgrounds. Analog Devices offers a pair of tools, LTspice IV and LTpowerCAD II to help designers tackle these challenges.The LTspice schematic capture and simulation tool offers a powerful aid to system designers in understanding the operation of an analog circuit and visualizing its waveforms and dynamic performance. LTspice is especially helpful in the following situations: When a user needs to develop a new circuit solution or unfamiliar supply topology If a user needs to understand or evaluate a new LTC product When a user needs to check a circuit’s dynamic behaviors and performancesHowever, because it is a general purpose simulation-oriented tool instead of design-oriented tool, LTspice has some limitations: For an inexperienced supply designer, the simulation waveforms do not provide sufficient explanations nor guide him with component selection and design trade-offs. For an experienced supply designers working on a familiar topology/solution with many repetitive designs, simulation may not be a necessary or productive design method. Instead, he really needs a spreadsheet tool to quickly calculate power supply parameters/values and estimate its performance. The LTspice simulation does not offer a detailed supply efficiency estimation and loss breakdown analysis, which can be very useful to select power components. LTspice does not offer a convenient , fast loop compensation design method for a switching mode supply. The user needs to either build his own small signal circuit model or do repetitive time-domain simulations with sinusoidal perturbation waveforms, which can be challenging and time consuming. As a complement to the LTspice simulationDownload LTspice XVII Gratis Halal

A p-channel device. It conducts current when a negative voltage (logic low) is applied to its gate terminal with respect to the source terminal. In CMOS, PMOS acts as pull up network in which the source is connected to VDD. When logic low(0) is applied is CMOS, the PMOS transistor turns on and connects the VDD to output which makes the output to logic high(1).NMOS: The NMOS transistor is an n-channel device. It conducts current when a positive voltage (logic high) is applied to its gate terminal with respect to the source terminal. In CMOS, MMOS acts as pull down network in which the source is connected to ground. When logic high(1) is applied is CMOS, the NMOS transistor turns on and connects the output to ground which makes the output to logic low(0).ObjectivesThe main goal of this project are given belowTo plot the schematics of logic gates, and circuitsTo plot the output waveformTo verify the functionalityProject StructureTool : LTspiceTechnology : C5N technologyLTspice Simulation Files: Files with .asc extension represents LTspice simulation files for each logic gate.AND.asc : LTspice simulation file for the AND gate.OR.asc : LTspice simulation file for the OR gate.NOT.asc : LTspice simulation file for the NOT gate.NAND.asc : LTspice simulation file for the NAND gate.NOR.asc : LTspice simulation file for the NOR gate.Circuit DetailsThe output of AND gate produces 1 if and only if all the input states are 1 else it produces 0. The logic symbol and truth table of 2-input AND gate is shown below. Figure 1: Logic Symbol, Truth table and Logic Circuit of AND gateThe output of OR gate produces 1 if one or more input states are 1 else it produces 0. The logic symbol and truth table of 2-input OR gate is shown below. Figure 2: Logic Symbol, Truth tableThe LTSpice XVII Simulator : Commands and Applications

Puppy Bowl XXI See Photos Meet the Players of Puppy Bowl XXI Read More Get Ready for Puppy Bowl XXI on Animal Planet! Buffalo Bills' Keon Coleman Hangs With Rescue Puppies For Puppy Bowl XXI! Puppy Bowl XXI Gameday Ready Look Back: Past Puppy Bowls Meet the Players of Puppy Bowl XX Baltimore Ravens Hang With Rescue Puppies for Puppy Bowl XX! Meet the Players of Puppy Bowl XIX By: Puppy Bowl Puppy Bowl XVIII Post Game Photos By: Puppy Bowl Congratulations to Kirby the MVP Winner of Puppy Bowl XVIII By: Puppy Bowl Meet the Players of Puppy Bowl XVIII By: Puppy Bowl Puppy Bowl XVII: Post Game Highlights By: Puppy Bowl Puppy Bowl XVII: Meet the Starting Line Up By: Puppy Bowl PUPPY BOWL XVII's Most Valuable Napper: Chunky Monkey By: Puppy Bowl Puppy Bowl Star Jett Stole the Hearts of Fans By: Puppy Bowl Meet Marshall! Puppy Bowl XVII MVP and Pupularity Playoffs Winner By: Puppy Bowl Look Back: Kitty Halftime Purrformances Puppy Bowl XVIII: Kitty Halftime Show Highlights A Retrospective: Kitty Halftime Show Rehearsals XVIITHE LTSPICE XVII SIMULATOR: Commands and Applications

Server will runthe simulation and return the results to the client. The client on the remote machine is a script instancing theSimClient class. An example of its usage is shown below:import osimport zipfileimport logging# In order for this, to work, you need to have a server running. To start a server, run the following command:# python -m spicelib.scripts.run_server --port 9000 --parallel 4 --output ./temp LTSpice 300_logger = logging.getLogger("spicelib.SimClient")_logger.setLevel(logging.DEBUG)from spicelib.client_server.sim_client import SimClientserver = SimClient(' 9000)print(server.session_id)runid = server.run("./testfiles/testfile.net")print("Got Job id", runid)for runid in server: # Ma zip_filename = server.get_runno_data(runid) print(f"Received {zip_filename} from runid {runid}") with zipfile.ZipFile(zip_filename, 'r') as zipf: # Extract the contents of the zip file print(zipf.namelist()) # Debug printing the contents of the zip file zipf.extract(zipf.namelist()[0]) # Normally the raw file comes first os.remove(zip_filename) # Remove the zip fileserver.close_session()-- in examples/sim_client_example.py [SimClient Example]usage: run_server [-h] [-p PORT] [-o OUTPUT] [-l PARALLEL] simulatorRun the LTSpice Server. This is a command line interface to the SimServer class. The SimServer class is used to runsimulations in parallel using a server-client architecture. The server is a machine that runs the SimServer class andthe client is a machine that runs the SimClient class. The argument is the simulator to be used (LTSpice, Ngspice, XYCE, etc.)positional arguments: simulator Simulator to be used (LTSpice, Ngspice, XYCE, etc.)optional arguments: -h, --help show this help message and exit -p PORT, --port PORT Port to run the server. Default is 9000 -o OUTPUT, --output OUTPUT Output folder for the results. Default is the current folder -l PARALLEL, --parallel PARALLEL Maximum number of parallel simulations. Default is 4asc_to_qsch.exeConverts LTspice schematics into QSPICE schematics.Usage: asc_to_qsch [options] ASC_FILE [QSCH_FILE]Options: --version show program's version number and exit -h, --help show this help message and exit -a PATH, --add=PATH Add a path for searching for symbolsOther functionslog\semi_dev_op_reader.opLogReaderThis module is used to read from LTSpice log. LTspice XVII: Subcircuit pin names in Operating Point analysis. 2. LTspice XVII solving Thevenin Resistance basics. 0. Add LTspice IV library to LTspice XVII. 0. LTSpice:

LTspice XVII Library einbinden. - Mikrocontroller.net

Boundary-scarred Capsuleers,Signups for Alliance Tournament XVII are now open! Below is the full list of rules and signup instructions. All hopeful competitors, please take your time and review everything carefully.ContentsAlliance Tournament XVII Rules & FormatIntroduction: Format & RegistrationFormatMercenary RuleParticipation & RegistrationSilent AuctionFeeder TournamentRulesSummary of Key Changes from previous ATsMatch RulesPenaltiesShip RulesShip Point ValuesPlace & TacticsFitting RestrictionsFlagshipsVictory ConditionsShip BansAdditional Rule Variation for the Final DayCollusion RulesAlliance Tournament XVII Rules & FormatGreetings Alliance Tournament competitors and fans. The format and rules for this year’s Alliance Tournament are similar to that of previous years. However, there have been some alterations to the overall ruleset so please peruse these rules carefully. For any questions or clarifications, you may post in the EVE Online Tournament Forum or the Alliance Tournament Discord server.Do note that both the format and match rules are subject to change at CCP’s discretion. It is strongly advised that participants regularly check the Tournament forums and Discord for the most up-to-date information.INTRODUCTION: FORMAT & REGISTRATIONFORMATAlliance Tournament XVII is a 32 team, double-elimination tournament hosted on Tranquility. The Tournament will culminate in a best-of-five finale, with the semi-final matches being a best-of-three series. The 32 entry slots will be decided in the following fashion:Maximum of 8 slots reserved for the winning captains from both the EVE NT Alliance Open and the Anger Games (4 slots per tournament)Maximum of 8 slots from the Feeder Tournament (see “Feeder Tournament” below)Remaining slots awarded to winners of the silent auction (see “Silent Auction” below)For AT XVII, the Captains directly invited are:TheLastSpartondexter xioAzure and ArgentMira ChieveDamassys KadeshStarFleetCommanderEach team will consist of a maximum of 10 pilots fielded at any given time. All alliance members are eligible to compete in any match in which their alliance is taking part; team lineups do not have to remain the same between games. Further, each ship is given a point value (listed below), and the sum of the point values for the ships must not exceed 100 points.Players may only compete for a single alliance, regardless of how many player accounts they have. Likewise, there shall be no sharing of in-game assets, information, or services with the intent to participate in, or assist, multiple teams. More on this in the “Collusion Rules” section.The seeding for AT XVII will be completely random, though in future tournaments the placing in AT XVII may be relevant. Players may not change their allegiance during AT XVII,LTspice XVII simulation - Q A - EngineerZone

To measure the rising temperature of their oven heated at full power.In a second step, when the whole system has reached the maximum temperature, we can cut the power and let it cool down (for this, we can open the branch of the heating element and adopt for initial conditions a high value for Tsystem). We then get the pattern shown in Figure 10.Correlation of real measurements in these two conditions with simulation results should bring realistic values for the system characteristics.And this is made even easier as the practical measurement data can be imported into LT spice and compared with the simulation results.Figure 9 Figure 10 Conclusion In conclusion, we can state that the principles developed in this article (PID, LTSpice, and a thermistor driven by temperature) are likely to help a designer of thermal applications to theoretically define the base of their application. With the help of a few characterizations of his system (thermal mass and dissipation), it will be possible to theoretically define a complete application before implementation.The diverse features of LT spice (measurement directives, worst case analysis, possibility to import real practical measurements into the software) together with the voltage driven NTC thermistor models are very useful tool to the temperature control designer.Of course, other simulation programs such as Simulink MATLAB might provide more readily available solutions, but as we have already said, LTSpice and temperature- / voltage-driven models are both completely free of charge. The quality / price ratio of the DIY method presented in this article is unbeatable.As usual, the simulation presented in this article is available on request at edesign.ntc@vishay.comReferences: Stas, A. “Old-School Analog Temperature Control Circuits Solved with Modern LTSpice Thermistor Dynamic Models, Part one.” Planet Analog. AspenCore, Feb. 21, 2017. Web. Feb. 2017.“Op Amp PID Controller.” eCircuit Center. Web. Feb. 2017.“LTSpice. LTspice XVII: Subcircuit pin names in Operating Point analysis. 2. LTspice XVII solving Thevenin Resistance basics. 0. Add LTspice IV library to LTspice XVII. 0. LTSpice: LTspice 2025 (Bản chuẩn cuối) - Download; LTspice xvii build oct 31 2025 - Download; LTspice xvii build sep 5 2025 - Download; LTspice xvii buildLTspice XVII keyboard shortcuts - DefKey

#2 The files supplied are specific to OrCAD, you'd be better off downloading a demo version of that. I like LTSpice, but if I am not mistaken the models are only Level 1. OrCAD PSPICE models are Level 3, and have a greater degree of complexity, so even if you spent a lot of time translating it would be an approximation of the original model.I had to something similar recently, with a transistor model given in Level 3 OrCAD format that I needed to port into LTSpice. It was tedious and time-consuming, and I had to refer to the datasheet for some parameters.Quite often it's best just to build the thing. But if you must have a simulation, then maybe make something from voltage-controlled switches and timers, that would be easier and give a pretty good approximation of the power supervisory IC you're after. Thank you very much... I was searching for a Linear Technologies IC which is atleast similar to the TPS3808 IC and I found this - LTC2930 which does the same function of the Texas IC but it monitors 6 different voltages. Although the Texas IC would have been perfect for my application, I can use the LTC2930 for simulation and checking whether my logic is correct. And the LTC2930 is included in the default LTSpice installation...Thank You Darren...Comments

The VDMOS model as used in LTspice simulator can model power MOSFET's nicely. Mike Engelhardt updated the VDMOS (May 2019) to include temperature parameters. I have updated my earlier IRF's and Exicon lateral's. They can be downloaded here for LTspice XVII OR LT-IV here. Updated Tutorial PDF for extracting parameters for the IRFP240 and IRFP9240. Download PDF below. A simple jig does pulse measurements (DIY breadboard it - may need Scope). Download PDF below. To simulate CMOS inverters eg for guitar overload effects then you need to use a MOSFET model with quasisaturation. The LTspice VDMOS lacks quasisaturation. It can be added using a subcircuit. Download PDF below. BTW SuperSpice already has a VDMOS with quasisaturation. My files are also provided free under Creative Commons 4 Attribution (over-riding my Copyright) and no liability is accepted. Please let me know if you find errors (use Contact). LTspice jigs for the 'VDMOS parameter extraction' Tutorial PDF (Part 1), Download "Compare-Extraction-jigs-IRFP240-IRFP9240.zip" has 6 LTspice jigs here. Part 1 only (1v6) Hegglun_VDMOS-parameter-extraction-Part- Adobe Acrobat Document 640.9 KB Part 1+2 (version 1v7) Hegglun_VDMOS-parameter-extraction-Part- Adobe Acrobat Document 1.3 MB Pulse tester jig Ver 1v0 Hegglun_Simple-pulse-jig-for-power-MOSFE Adobe Acrobat Document 441.2 KB LTspice files below for the 'Simple pulse jig for power MOSFETs' : Download "VDMOS+EKV-10x20+20x20" LTspice jigs and Spreadsheet here. Download "VDMOS-20N20+20P20-measured-data" here. Dec 2021 superseded: Subcircuit to add Quasisaturation to the VDMOS (Ver 0v1) white paper here and LTspice demo files here Triode+SIT+jFET subcircuit using the VDMOS Dec 2021: This is an ambitious subcircuit! I may change it into 3 separate versions some day. updated white paper here. models and demo jig here. Update Jan 2023 This VDMOS subcircuit models jFET's, SIT's and Triode's, it adds effects including: Gate-drain leakage current (IGSX) that changes with Vds and temperature Quasisaturation for jFET's is significant for most small-signal jFET plots Noise and breakdown parameters are also included Triode (SIT) Mu varies with Vgk (Vgs) and Vak (Vds), and Triode positive grid current is modulated by Vak Update Jan 2023 TriJmos-Triode-and-jFET-model-using-the- Adobe Acrobat Document 839.7 KB

2025-04-04Object such as alist or a generator as a second argument.When the run_all() method is called, it will make run a simulation per each combination of values. On the example aboveit will make the simulations:(XU1, V1) in (("AD712", 5), ("AD712", 10), ("AD712", 15), ("AD820_ALT", 5), ("AD820_ALT", 10), ("AD820_ALT", 15))It should be noted that for each sweep method added it will add a new dimension simulation space.In other words, the total number of simulations will be the product of each vector length. There is no restriction tothe number of simulations to be done, however, a huge number of simulation will take a long time to execute and mayoccupy a considerable amount of space on the disk.Simulators and Windows, Linux and MacOS compatibilityThe LTspice class tries to detect the correct path of the LTspice installation depending on the platform. On Linuxit expects LTspice to be installed under wine. On MacOS, it first looks for LTspice installed under wine, and when itcannot be found, it will look for native LTspice. The reason is that the command line interface of the native LTspice isseverely limited.If you use the native LTspice, please make sure that you have installed the libraries via Settings: Operationtab, Model Update button.Ngspice runs natively under Windows, Linux and MacOS (via brew). This library works with Ngspice CLI, and tries todetect the correct executable path, no matter the platform. It cannot (yet) work with the shared library version ofNgspice that is delivered with for example Kicad, you will need to install the CLI version. You can however use Kicad asthe schema editor and subsequently save the Ngspice netlist to use it with this library.For the other simulators, built-in Linux/MacOS support is coming, but you can always try to use it under Linux viasetting of the executable paths.Executable and Library pathsA large variety

2025-04-12Today’s electronics systems require an increasing number of power rails and supply solutions, with the load range from a few mA for standby supply to over 100A for ASIC or FPGA core voltage regulators. It is important to have the appropriate solutions for the targeted applications and meet specified performance requirements, such as high efficiency, high reliability, tight printed circuit board (PCB) space, accurate output regulation, fast transient response, and low solution cost. Power management design, especially embedded switching mode supply design, is becoming a more frequent and challenging task for system designers, who may or may not have strong power supply backgrounds. Analog Devices offers a pair of tools, LTspice IV and LTpowerCAD II to help designers tackle these challenges.The LTspice schematic capture and simulation tool offers a powerful aid to system designers in understanding the operation of an analog circuit and visualizing its waveforms and dynamic performance. LTspice is especially helpful in the following situations: When a user needs to develop a new circuit solution or unfamiliar supply topology If a user needs to understand or evaluate a new LTC product When a user needs to check a circuit’s dynamic behaviors and performancesHowever, because it is a general purpose simulation-oriented tool instead of design-oriented tool, LTspice has some limitations: For an inexperienced supply designer, the simulation waveforms do not provide sufficient explanations nor guide him with component selection and design trade-offs. For an experienced supply designers working on a familiar topology/solution with many repetitive designs, simulation may not be a necessary or productive design method. Instead, he really needs a spreadsheet tool to quickly calculate power supply parameters/values and estimate its performance. The LTspice simulation does not offer a detailed supply efficiency estimation and loss breakdown analysis, which can be very useful to select power components. LTspice does not offer a convenient , fast loop compensation design method for a switching mode supply. The user needs to either build his own small signal circuit model or do repetitive time-domain simulations with sinusoidal perturbation waveforms, which can be challenging and time consuming. As a complement to the LTspice simulation

2025-04-18A p-channel device. It conducts current when a negative voltage (logic low) is applied to its gate terminal with respect to the source terminal. In CMOS, PMOS acts as pull up network in which the source is connected to VDD. When logic low(0) is applied is CMOS, the PMOS transistor turns on and connects the VDD to output which makes the output to logic high(1).NMOS: The NMOS transistor is an n-channel device. It conducts current when a positive voltage (logic high) is applied to its gate terminal with respect to the source terminal. In CMOS, MMOS acts as pull down network in which the source is connected to ground. When logic high(1) is applied is CMOS, the NMOS transistor turns on and connects the output to ground which makes the output to logic low(0).ObjectivesThe main goal of this project are given belowTo plot the schematics of logic gates, and circuitsTo plot the output waveformTo verify the functionalityProject StructureTool : LTspiceTechnology : C5N technologyLTspice Simulation Files: Files with .asc extension represents LTspice simulation files for each logic gate.AND.asc : LTspice simulation file for the AND gate.OR.asc : LTspice simulation file for the OR gate.NOT.asc : LTspice simulation file for the NOT gate.NAND.asc : LTspice simulation file for the NAND gate.NOR.asc : LTspice simulation file for the NOR gate.Circuit DetailsThe output of AND gate produces 1 if and only if all the input states are 1 else it produces 0. The logic symbol and truth table of 2-input AND gate is shown below. Figure 1: Logic Symbol, Truth table and Logic Circuit of AND gateThe output of OR gate produces 1 if one or more input states are 1 else it produces 0. The logic symbol and truth table of 2-input OR gate is shown below. Figure 2: Logic Symbol, Truth table

2025-04-13